# 3/4-Cell Lithium-Ion/Polymer Protector

#### **Features**

- High Detection Accuracy

- -Over-charge Detection: ±25mV

- -Over-discharge Detection: ±80mV

- -Discharge Over-current Detection: ±25mV

- Discharge Over-current Protection

- High Withstand Voltage

- -Absolute maximum ratings: 40V (VDD VSS)

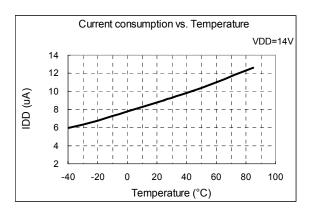

- Low Supply Current

- -Supply current: 9μA (Typ.)

- -Standby current: 0.1μA (Max.) (Power Down Mode)

- Three Types of Current Protections

- Ultra Small Package

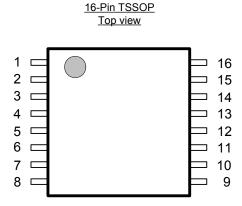

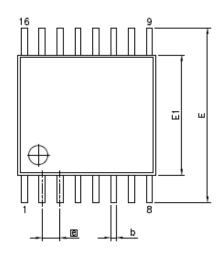

- -TSSOP-16L

## **Description**

The NT1775 protects lithium-ion/lithium-polymer rechargeable battery in the abnormal events of over-charge, over-discharge, discharging over-current and for a 3/4-cell lithium-ion/lithium polymer battery pack.

If any of above abnormal conditions occurred. NT1775 would turn off the MOSFETs to protect battery.

NT1775 would enter power down mode when over-discharge protection occurs to minimize the current consumption.

In general, NT1775 can be restored to normal mode after short-circuit or reversely charging is removed. To avoid hiccup reaction as protection is activated due to the serious short-circuit and reversely-charging conditions, NT1775 may enter power down mode sometimes. It can be awaked with charger reconnection.

The tiny package of 16 pin TSSOP is especially suitable for the battery packs in portable devices.

## **Applications**

- Lithium-ion rechargeable battery packs

- Lithium-polymer rechargeable battery packs

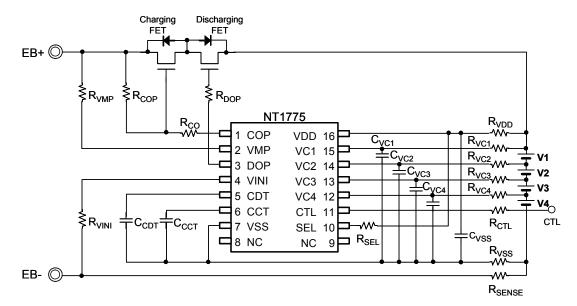

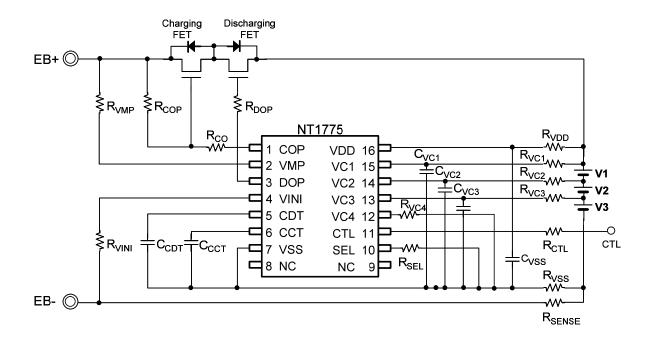

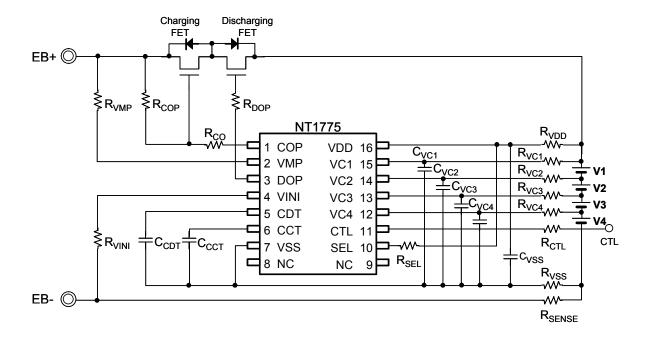

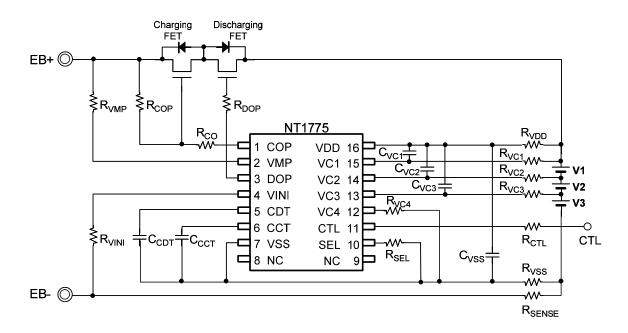

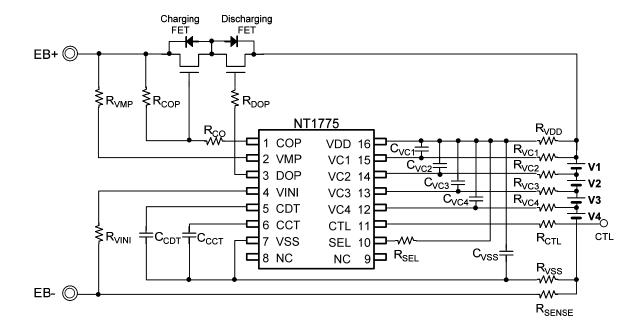

## **Typical Application Circuit**

These devices have limited build-in ESD protection. The leads must be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

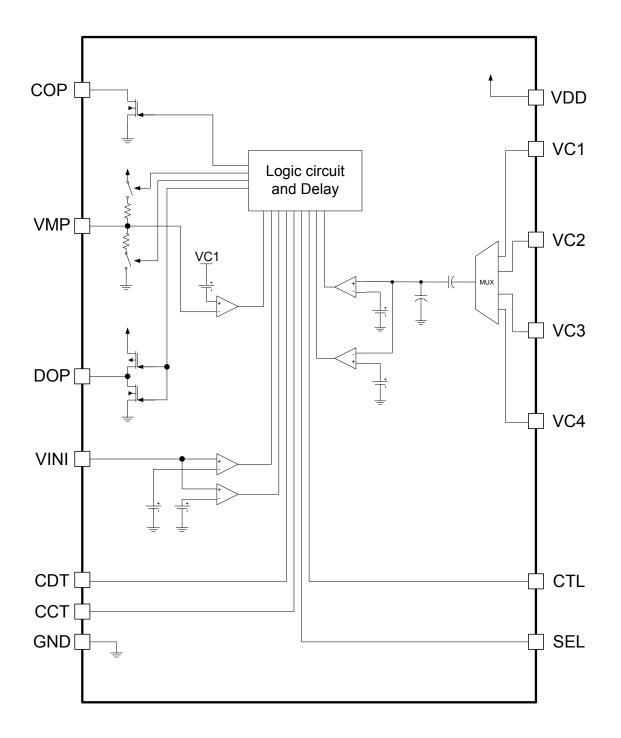

# **Block Diagram**

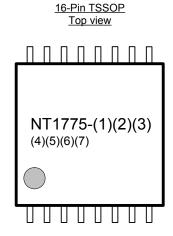

# Package and Pin Configurations

| Pin No. | Symbol | Pin description                                                                        |  |  |  |  |

|---------|--------|----------------------------------------------------------------------------------------|--|--|--|--|

| 1       | COP    | FET gate control pin for charging path (Nch open-drain output)                         |  |  |  |  |

| 2       | VMP    | oltage detction pin between VC1 and VMP (Short-circuit detection pin)                  |  |  |  |  |

| 3       | DOP    | ET gate control pin for discharging path (CMOS output)                                 |  |  |  |  |

| 4       | VINI   | Voltage detction pin between VSS and VINI (Over-current 1,2 detection pin)             |  |  |  |  |

| 5       | CDT    | Capacitor connection for over-discharge detection, over-current detection 1 delay time |  |  |  |  |

| 6       | ССТ    | Capacitor connection for over-charge detection delay time                              |  |  |  |  |

| 7       | VSS    | Negative power input pin                                                               |  |  |  |  |

| 8       | NC     | No connection                                                                          |  |  |  |  |

| 9       | NC     | No connection                                                                          |  |  |  |  |

| 10      | SEL    | Pin for switching 3cell/4cell series SEL pin=VSS: 3cell, SEL pin=VDD: 4cell            |  |  |  |  |

|         |        | Control of charge FET and discharge FET                                                |  |  |  |  |

|         |        | CTL Pin COP Pin DOP Pin                                                                |  |  |  |  |

| 11      | CTL    | High Hi-Z VDD                                                                          |  |  |  |  |

|         |        | Open Hi-Z VDD                                                                          |  |  |  |  |

|         |        | Low Normal status* Normal status*                                                      |  |  |  |  |

| 12      | VC4    | Cell V4 positive voltage and cell 3 negative voltage input pin                         |  |  |  |  |

| 13      | VC3    | Cell V3 positive voltage and cell 2 negative voltage input pin                         |  |  |  |  |

| 14      | VC2    | Cell V2 positive voltage and cell 1 negative voltage input pin                         |  |  |  |  |

| 15      | VC1    | Cell V1 positive voltage input pin                                                     |  |  |  |  |

| 16      | VDD    | Power supply input pin                                                                 |  |  |  |  |

# **Ordering Information**

## **Product version code**

| Product<br>Name | Version<br>Code | Package<br>Type | Over-<br>charge<br>Detection<br>Voltage<br>(V <sub>OV</sub> ) | Over-<br>charge<br>Release<br>Voltage<br>(V <sub>REL1</sub> ) | Over-<br>discharge<br>Detection<br>Voltage<br>(V <sub>OD</sub> ) | Over-<br>discharge<br>Release<br>Voltage<br>(V <sub>REL2</sub> ) | Discharge<br>Over-current<br>Detection<br>Voltage 1<br>(V <sub>DOC1</sub> ) | 0V<br>Battery<br>Charge<br>Function |

|-----------------|-----------------|-----------------|---------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------|

| NT1775          | LNG             | Q1              | 4.225V                                                        | 4.075V                                                        | 2.4V                                                             | 3.0V                                                             | 0.20V                                                                       | Available                           |

| NT1775          | JPM             | Q1              | 4.275V                                                        | 4.075V                                                        | 2.3V                                                             | 2.7V                                                             | 0.13V                                                                       | Available                           |

| NT1775          | GNG             | Q1              | 4.300V                                                        | 4.150V                                                        | 2.4V                                                             | 3.0V                                                             | 0.20V                                                                       | Available                           |

| NT1775          | ENK             | Q1              | 4.350V                                                        | 4.150V                                                        | 2.4V                                                             | 3.0V                                                             | 0.15V                                                                       | Available                           |

| NT1775          | EXG             | Q1              | 4.350V                                                        | 4.150V                                                        | 2.4V                                                             | 3.0V                                                             | 0.20V                                                                       | Available                           |

| NT1775          | DNX             | Q1              | 4.400V                                                        | 4.200V                                                        | 2.4V                                                             | 3.0V                                                             | 0.17V                                                                       | Available                           |

# **Marking Information**

(1)(2)(3) : Version Code (4)(5)(6)(7) : Lot Number

| Product name | Version code : (1)(2)(3) |

|--------------|--------------------------|

| NT1775-LNGQ1 | LNG                      |

| NT1775-JPMQ1 | JPM                      |

| NT1775-GNGQ1 | GNG                      |

| NT1775-ENKQ1 | ENK                      |

| NT1775-EXGQ1 | EXG                      |

| NT1775-DNXQ1 | DNX                      |

# **Absolute Maximum Ratings**

(Ta = 25°C unless otherwise specified)

| Symbol           | Descriptions                                                | Rating                 | Unit |

|------------------|-------------------------------------------------------------|------------------------|------|

| $V_{DS}$         | Input voltage between VDD and VSS                           | VSS - 0.3 to VSS + 40  | V    |

|                  | Input voltage of (VC1-GND), (VC2-GND), (VC3-GND)            | VSS - 0.3 to VDD + 0.3 | V    |

| V <sub>IN</sub>  | Input voltage of (VC1-VC2), (VC2-VC3), (VC3-VC4), (VC4-GND) | VSS - 0.3 to VSS + 8.0 | V    |

|                  | Input voltage range of CTL and SEL pin                      | VSS – 0.3 to VDD + 0.3 | V    |

|                  | Input voltage range of CCT, CDT and VINI pin                | VSS - 0.3 to VSS + 8.0 | V    |

| $V_{VMP}$        | Input voltage range of VMP pin                              | VSS - 0.3 to VSS + 40  | V    |

| $V_{CO}$         | Output voltage range of COP pin                             | VSS - 0.3 to VSS + 40  | V    |

| $V_{DO}$         | Output voltage range of DOP pin                             | VSS - 0.3 to VDD + 0.3 | V    |

| $P_D$            | Power Dissipation                                           | 400                    | mV   |

| T <sub>OPT</sub> | Operating Temperature Range                                 | -40 to +85             | °C   |

| T <sub>STG</sub> | Storage Temperature range                                   | -40 to 125             | °C   |

Applying any over "Absolute Maximum Ratings" practice can permanently damage the device. These data are indicated the absolute maximum values only but not implied any operating performance.

## **Electrical Characteristics**

(Ta = 25°C unless otherwise specified)

| Symbol             | Item                                          | Conditions                  | MIN                         | TYP               | MAX                         | Unit |

|--------------------|-----------------------------------------------|-----------------------------|-----------------------------|-------------------|-----------------------------|------|

| Detectio           | Detection Voltage                             |                             |                             |                   |                             |      |

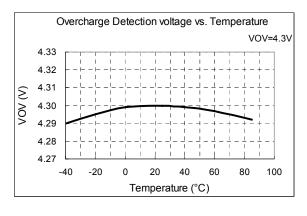

| V <sub>ov</sub>    | Over-charge detection voltage                 | -                           | V <sub>OV</sub><br>-0.025   | V <sub>ov</sub>   | V <sub>OV</sub><br>+0.025   | ٧    |

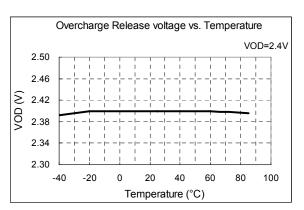

| V <sub>REL1</sub>  | Over-charge release voltage                   | -                           | V <sub>REL1</sub><br>-0.050 | $V_{REL1}$        | V <sub>REL1</sub> +0.050    | ٧    |

| V <sub>OD</sub>    | Over-discharge detection voltage              | _                           | V <sub>OD</sub><br>-0.080   | V <sub>OD</sub>   | V <sub>OD</sub><br>+0.080   | ٧    |

| $V_{REL2}$         | Over-discharge release voltage                | _                           | V <sub>REL2</sub><br>-0.100 | $V_{REL2}$        | V <sub>REL2</sub><br>+0.100 | ٧    |

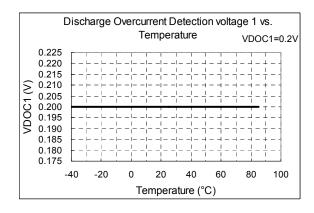

| V <sub>DOC1</sub>  | Discharge over-current detection voltage 1    | -                           | V <sub>DOC1</sub><br>-0.025 | V <sub>DOC1</sub> | V <sub>DOC1</sub> +0.025    | ٧    |

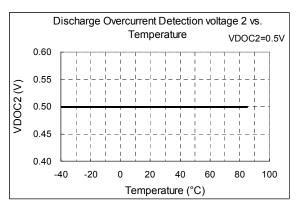

| V <sub>DOC2</sub>  | Discharge over-current detection voltage 2    | _                           | 0.4                         | 0.5               | 0.6                         | ٧    |

| $V_{SHORT}$        | Short-circuit detection voltage               | VC1 reference               | -1.5                        | -1.2              | -0.9                        | V    |

| Delay Ti           | me                                            |                             |                             |                   |                             |      |

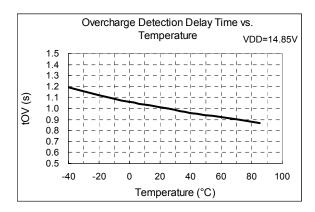

| t <sub>ov</sub>    | Output delay time of over-charge              | CCT pin capacitance=0.1μF   | 0.5                         | 1.0               | 1.5                         | S    |

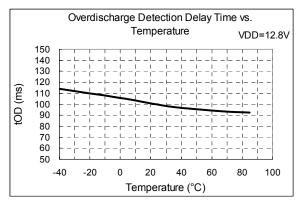

| t <sub>od</sub>    | Output delay time of over-discharge           | CDT pin capacitance=0.1μF   | 50                          | 100               | 150                         | ms   |

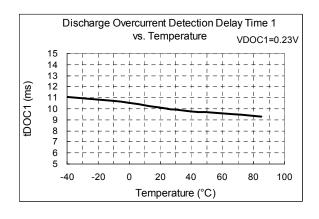

| t <sub>DOC1</sub>  | Output delay time of discharge over current 1 | CDT pin capacitance=0.1μF   | 5                           | 10                | 15                          | ms   |

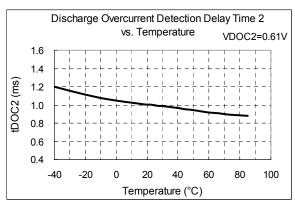

| t <sub>DOC2</sub>  | Output delay time of discharge over current 2 | -                           | 0.4                         | 1.0               | 1.6                         | ms   |

| t <sub>short</sub> | Output delay time of short-circuit detection  | FET gate capacitance=2000pF | 50                          | 300               | 600                         | μS   |

6/26

# **Electrical Characteristics (continued)**

(Ta = 25°C unless otherwise specified)

|                   | (1a - 25 Culliess of                                |                                         | illei wise specilled |     |         |                |

|-------------------|-----------------------------------------------------|-----------------------------------------|----------------------|-----|---------|----------------|

| Symbol            | Item                                                | Conditions                              | MIN                  | TYP | MAX     | Unit           |

| Current           | Consumption                                         |                                         |                      |     |         |                |

| I <sub>DD</sub>   | Supply current                                      | V1=V2=V3=V4=3.5V                        | _                    | 9   | 15      | μА             |

| I <sub>PDN</sub>  | Current consumption at power down                   | V1=V2=V3=V4=1.5V                        | -                    | _   | 0.1     | μА             |

| I <sub>VC1</sub>  | VC1 pin current                                     | V1=V2=V3=V4=3.5V                        | -0.3                 | 0.5 | 1       | μΑ             |

| I <sub>VC2</sub>  | VC2 pin current                                     | V1=V2=V3=V4=3.5V                        | -0.3                 | 0   | 0.3     | μΑ             |

| I <sub>VC3</sub>  | VC3 pin current                                     | V1=V2=V3=V4=3.5V                        | -0.3                 | 0   | 0.3     | μA             |

| I <sub>VC4</sub>  | VC4 pin current                                     | V1=V2=V3=V4=3.5V                        | -0.3                 | 0   | 0.3     | μA             |

| I <sub>CTLH</sub> | CTL pin current "H"                                 | V1=V2=V3=V4=3.5V, V <sub>CTL</sub> =VDD | _                    | _   | 0.1     | μA             |

| I <sub>CTLL</sub> | CTL pin current "L"                                 | V1=V2=V3=V4=3.5V, V <sub>CTL</sub> =VSS | -0.8                 | _   | _       | μA             |

| I <sub>SELH</sub> | SEL pin current "H"                                 | V1=V2=V3=V4=3.5V, V <sub>SEL</sub> =VDD | _                    | _   | 0.1     | <u>.</u><br>μΑ |

| I <sub>SELL</sub> | SEL pin current "L"                                 | V1=V2=V3=V4=3.5V, V <sub>SEL</sub> =VSS | -0.1                 | _   | _       | μА             |

| Input Vo          |                                                     | , old                                   |                      |     |         | r-             |

| V <sub>DSOP</sub> | Operating voltage between VDD and VSS               | Output voltage of COP and DOP fixed     | 4.0                  | _   | 26.0    | V              |

| V <sub>CTLH</sub> | CTL input voltage "H"                               | _                                       | 2.7                  | _   | _       | V              |

| V <sub>CTLL</sub> | CTL input voltage "L"                               | _                                       | _                    | _   | 1.0     | ٧              |

| $V_{SELH}$        | SEL input voltage "H"                               | _                                       | VDD×0.8              | _   | _       | ٧              |

| V <sub>SELL</sub> | SEL input voltage "L"                               | _                                       | _                    | _   | VDD×0.2 | V              |

| 0V Batte          | ry Charging Function                                |                                         |                      |     | •       |                |

| V <sub>0CHA</sub> | 0V battery charge starting charger voltage          | 0V battery charging available           | _                    | 1.6 | 2.0     | V              |

| Output C          | Current                                             |                                         |                      |     |         |                |

| Ісон              | COP pin leakage current                             | V <sub>COP</sub> =24V                   | _                    | _   | 0.1     | μА             |

| I <sub>COL</sub>  | COP pin sink current                                | V <sub>COP</sub> =VSS+0.5V              | 10                   | _   | _       | μA             |

| I <sub>DOH</sub>  | DOP pin source current                              | V <sub>DOP</sub> =VDD-0.5V              | 10                   | _   | _       | μA             |

| I <sub>DOL</sub>  | DOP pin sink current                                | V <sub>DOP</sub> =VSS+0.5V              | 10                   | _   | _       | μА             |

| VMP Inte          | ernal Resistance                                    |                                         |                      |     |         |                |

| R <sub>VMD</sub>  | Internal resistance between VMP and VDD             | V1=V2=V3=V4=3.5V                        | 0.5                  | 1.0 | 1.5     | МΩ             |

| R <sub>VMS</sub>  | Internal resistance between VMP and V <sub>SS</sub> | V1=V2=V3=V4=1.8V                        | 450                  | 900 | 1800    | ΚΩ             |

## **Measurement Methods**

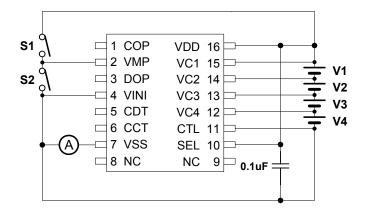

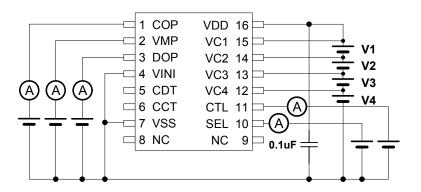

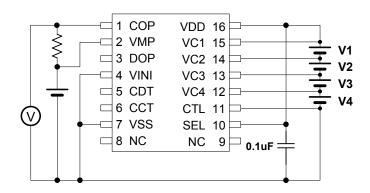

#### (1) Power consumption (Measurement circuit 1)

- 1) Set V1=V2=V3=V4=3.5V, S1=ON and S2=OFF, enter normal condition.

- 2) The measured current at VSS pin is the supply current ( $I_{DD}$ ).

- 3) Set V1=V2=V3=V4=1.5V, S1=OFF and S2=ON, enter power down mode.

- 4) The measured current at VSS pin is the current consumption at power down (I<sub>PDN</sub>).

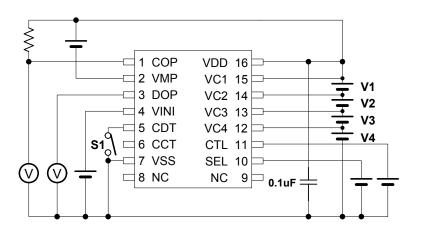

## (2) Over-charge detection and release voltage (Measurement circuit 2)

- 1) Set V1=V2=V3=V4=3.5V, V<sub>VMP</sub>=V<sub>SEL</sub>=VDD, V<sub>VINI</sub>=V<sub>CTL</sub>=0V and S1=OFF, enter normal condition.

- 2) Initialize V1 voltage from 3.5V and increase gradually. The V1 voltage is the over-charge detection voltage (V<sub>OV</sub>) when COP pin switches from low to high.

- 3) Decrease V1 gradually. The V1 voltage is the over-charge release detection voltage (V<sub>REL1</sub>) when COP pin switches from high to low.

- 4) When the voltage of Vn (n=2 to 4) is changed. The over-charge detection/release voltage can be determined in the same way as when n=1.

#### (3) Over-discharge detection and release voltage (Measurement circuit 2)

- 1) Set V1=V2=V3=V4=3.5V,  $V_{VMP}$ = $V_{SEL}$ =VDD,  $V_{VINI}$ = $V_{CTL}$ =0V and S1=OFF, enter normal condition.

- 2) Decrease V1 voltage from 3.5V gradually. The V1 voltage is the over-discharge detection voltage (V<sub>OD</sub>) when DOP pin switches from low to high.

- 3) Increase V1 gradually. When DOP pin switches from high to low, the V1 voltage is the over-discharge release detection voltage (V<sub>REL2</sub>).

- 4) When the voltage of Vn (n=2 to 4) is changed. The over-discharge detection/release voltage can be determined in the same way as when n=1.

#### (4) Discharge over-current detection voltage 1 (Measurement circuit 2)

- 1) Set V1=V2=V3=V4=3.5V,  $V_{VMP}=V_{SEL}=VDD$ ,  $V_{VINI}=V_{CTL}=0V$  and S1=OFF, enter normal condition.

- 2) Initialize  $V_{VINI}$  from 0V and increase gradually. When both COP and DOP pins switch from low to high, the  $V_{VINI}$  voltage is the discharge over-current detection voltage  $1(V_{DOC1})$ .

#### (5) Discharge over-current detection voltage 2 (Measurement circuit 2)

- 1) Set V1=V2=V3=V4=3.5V,  $V_{VMP}=V_{SEL}=VDD$ ,  $V_{VINI}=V_{CTL}=0V$  and S1=ON, enter normal condition.

- 2) Initialize  $V_{VINI}$  from 0V and increase gradually. When both COP and DOP pins switch from low to high, the  $V_{VINI}$  voltage is the discharge over-current detection voltage  $2(V_{DOC2})$ .

#### (6) Short-circuit detection voltage (Measurement circuit 2)

- 1) Set V1=V2=V3=V4=3.5V,  $V_{VMP}$ = $V_{SEL}$ =VDD,  $V_{VINI}$ = $V_{CTL}$ =0V and S1=OFF, enter normal condition.

- 2) Initialize  $V_{VMP}$  from VDD and decrease gradually. When both COP and DOP pins switch from low to high, the voltage of  $(V_{VMP} V_{VC1})$  is the short-circuit detection voltage  $(V_{SHORT})$ .

## (7) CTL input voltage "H" and "L" (Measurement circuit 2)

- 1) Set V1=V2=V3=V4=3.5V, V<sub>VMP</sub>=V<sub>SEL</sub>=VDD, V<sub>VINI</sub>=V<sub>CTL</sub>=0V and S1=OFF, enter normal condition.

- 2) Initialize  $V_{CTL}$  from 0V and increase gradually. When both COP and DOP pins switch from low to high, the  $V_{CTL}$  voltage is the CTL input voltage "H" ( $V_{CTLH}$ ).

- 3) Decrease  $V_{CTL}$  from VDD gradually. When both COP and DOP pins switch from high to Low, the  $V_{CTL}$  is the CTL input voltage "L" ( $V_{CTLL}$ ).

## (8) SEL input voltage "H" and "L" (Measurement circuit 2)

- 1) Set V1=V2=V3=3.5V, V4=0V,  $V_{VMP}$ = $V_{SEL}$ =VDD,  $V_{VINI}$ = $V_{CTL}$ =0V, S1=OFF, enter normal condition.

- 2) Decrease  $V_{SEL}$  from VDD gradually. When DOP pin switches from high to Low, the  $V_{SEL}$  is the SEL input voltage "L" ( $V_{SELL}$ ).

- 3) Initialize  $V_{SEL}$  from 0V and increase gradually. When DOP pin switches from low to high, the  $V_{SEL}$  voltage is the SEL input voltage "H" ( $V_{SELH}$ ).

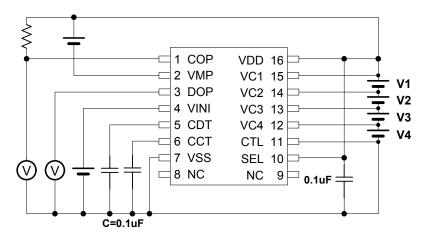

#### (9) Over-charge and over-discharge detection delay time (Measurement circuit 3)

- 1) Set V1=V2=V3=V4=3.5V,  $V_{VMP}$ =VDD,  $V_{VINI}$ =0V, enter normal condition.

- 2) Increase V1 from 3.5V to  $(V_{OV}+0.02V)$  immediately (within 10us). The over-charge detection delay time  $(t_{OV})$  is the period from the time V1 gets to  $(V_{OV}+0.02V)$  till COP pin switches from low to high.

- 3) Set V1=V2=V3=V4=3.5V, V<sub>VMP</sub>=VDD, V<sub>VINI</sub>=0V, enter normal condition.

- 4) Decrease V1 from 3.5V to  $(V_{OD}$ -0.02V) immediately (within 10us). The over-discharge detection delay time  $(t_{OD})$  is the period from the time V1 gets to  $(V_{OD}$ -0.02V) till DOP pin switches from low to high.

## (10) Discharge over-current and short-circuit detection delay time (Measurement circuit 3)

- 1) Set V1=V2=V3=V4=3.5V, V<sub>VMP</sub>=VDD, V<sub>VINI</sub>=0V, enter normal condition.

- 2) Increase  $V_{VINI}$  from 0V to  $(V_{DOC1}+10mV)$  immediately (within 10us). The discharge over-current detection delay time 1 ( $t_{DOC1}$ ) is the period from the time  $V_{VINI}$  gets to  $(V_{DOC1}+10mV)$  till COP and DOP pin switches from low to high.

- 3) Set V1=V2=V3=V4=3.5V,  $V_{VMP}$ =VDD,  $V_{VINI}$ =0V, enter normal condition.

- 4) Increase V<sub>VINI</sub> from 0V to (V<sub>DOC2</sub>+0.1V) immediately (within 10us). The discharge over-current detection delay time 2 (t<sub>DOC2</sub>) is the period from the time V<sub>VINI</sub> gets to (V<sub>DOC2</sub>+0.1V) till COP and DOP pin switches from low to high.

- 5) Set V1=V2=V3=V4=3.5V, V<sub>VMP</sub>=VDD, V<sub>VINI</sub>=0V, enter normal condition.

- 6) Decrease  $V_{VMP}$  from VDD to ( $V_{SHORT}$ -0.2V) immediately (within 10us). The short detection delay time ( $t_{SHORT}$ ) is the period from the time  $V_{VMP}$  gets to ( $V_{SHORT}$ -0.2V) till COP and DOP pin switches from low to high.

## (11) Internal resistance (Measurement circuit 4)

- 1) Set V1=V2=V3=V4=3.5V, V<sub>VMP</sub>=V<sub>SEL</sub>=VDD, V<sub>CTL</sub>=0V, COP and DOP pin left "open".

- 2) Decrease VMP voltage to 0V. VDD/I<sub>VMD</sub> is the internal resistance between VDD and VMP (R<sub>VMD</sub>).

- 3) Set V1=V2=V3=V4=3.5V, V<sub>VMP</sub>=V<sub>SEL</sub>=VDD, V<sub>CTL</sub>=0V, COP and DOP pin left "open".

- 4) Decrease V1=V2=V3=V4=1.8V.  $VDD/I_{VMS}$  is the internal resistance between VSS and VMP (R<sub>VMS</sub>). \* Using the current value of the VMP pin.

## (12) CTL pin "H", "L" current, SEL pin "H", "L" current (Measurement circuit 4)

- 1) Set V1=V2=V3=V4=3.5V, V<sub>VMP</sub>=V<sub>SEL</sub>=VDD, V<sub>CTL</sub>=0V, COP and DOP pin left "open". The current flowing through the CTL pin is the CTL pin current "L" (I<sub>CTLL</sub>). Then, set V<sub>CTL</sub>=VDD, the current flowing through the CTL pin is the CTL pin current "H" (I<sub>CTLH</sub>).

- 2) Set V1=V2=V3=V4=3.5V,  $V_{VMP}=V_{SEL}=VDD$ ,  $V_{CTL}=0V$ , COP and DOP pin left "open". The current flowing through the SEL pin is the SEL pin current "H" ( $I_{SELH}$ ). Then, set  $V_{SEL}=0V$ , the current flowing through the SEL pin is the SEL pin current "L" ( $I_{SELL}$ ).

#### (13) COP pin leakage and sink current, DOP pin source and sink current (Measurement circuit 4)

- 1) Set V1=V2=V3=V4=3.5V,  $V_{VMP}=V_{SEL}=VDD$ ,  $V_{CTL}=0V$ ,  $V_{COP}=0.5V$ , DOP pin left "open". The current flowing through the COP pin is the COP pin sink current ( $I_{COL}$ ).

- 2) Set V1=V2=V3=V4=6V,  $V_{VMP}=V_{SEL}=V_{COP}=VDD$ ,  $V_{CTL}=0V$ , DOP pin left "open". The current flowing through the COP pin is the COP pin leakage current ( $I_{COH}$ ).

- 3) Set V1=V2=V3=V4=3.5V,  $V_{VMP}=V_{SEL}=VDD$ ,  $V_{CTL}=0V$ ,  $V_{DOP}=0.5V$ , COP pin left "open". The current flowing through the DOP pin is the DOP pin sink current ( $I_{DOL}$ ).

- 4) Set V1=V2=V3=V4=3.5V,  $V_{SEL}$ =VDD,  $V_{CTL}$ =0V,  $V_{VMP}$ =VDD-2V,  $V_{DOP}$ =VDD-0.5V, COP pin left "open". The current flowing through the DOP pin is the DOP pin source current ( $I_{DOH}$ ).

## (14) **0V charge starting voltage** (Measurement circuit 5)

1) Set V1=V2=V3=V4=0V, increase  $V_{VMP}$  from 0V gradually. The  $V_{VMP}$  voltage is the 0V charge starting voltage ( $V_{0CHA}$ ) when COP pin voltage is 1V lower than the  $V_{VMP}$  voltage.

#### Measurement circuit 1

Measurement circuit 2

Measurement circuit 3

Measurement circuit 4

Measurement circuit 5

## **Operations**

The NT1775 provides over-charge, over-discharge, discharge over-current, and short circuit protections for the 3/4-cell battery pack. When the battery pack is in charging stage, the current flow is from EB+ to EB- through the batteries. NT1775 continuously senses all the battery voltage by VC1~VC4 pins if the over-charge occurs. On the other hand, when the battery pack is in discharging stage, the current flow is from EB+ to EB- through the load. NT1775 also senses all battery voltages by VC1~VC4 pins if the over-discharge occurs. As discharging, there is a positive voltage between VSS and EB-, because the current passing through R<sub>SENSE</sub>. NT1775 detects this positive voltage by VINI pin if the discharge over-current occurs as well. Further, NT1775 also provide a short protection by detecting the voltage drop between VDD and VMP pins.

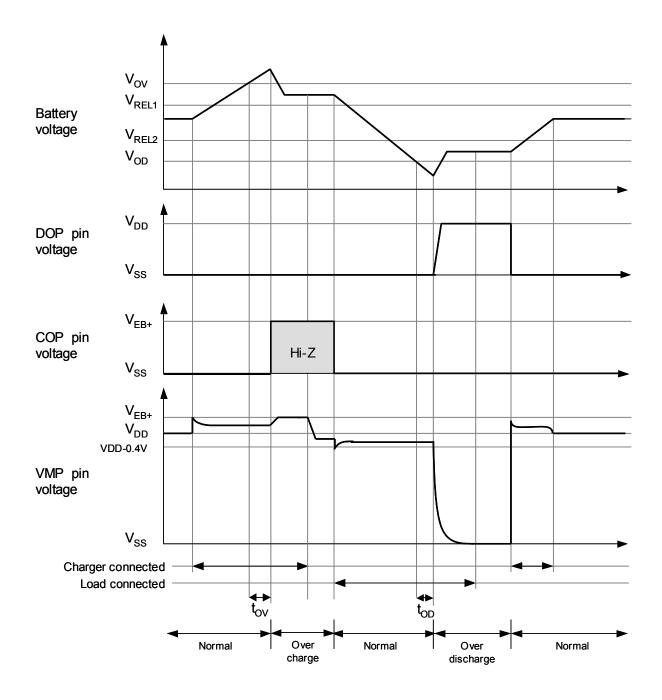

#### (1) Over-charge Condition

1) Over-charge Protection

When any of the cells voltage is equal to or higher than the over-charge detection voltage  $(V_{OV})$  for a certain delay time  $(t_{OV})$ , NT1775 would turn off the external Pch MOSFET by COP pin to protect the pack from being over-charged. In the meanwhile, COP pin turns to "H" from "L" level.

2) Over-charge Protection Release

The over-charge protection can be released by either of the following conditions,

- (a) Removed charger and connect a load (100K $\Omega$  typically) when all battery voltages are lower than the detection voltage  $V_{\text{OV}}$

- (b) All battery voltages are lower than the over-charge release voltages V<sub>REL1</sub>.

## (2) Over-discharge Condition

1) Over-discharge Protection

When any of the cells is lower than the over-discharge detection voltage  $(V_{\text{OD}})$  for a certain delay time  $(t_{\text{OD}})$ , NT1775 would turn off the external Pch MOSFET by DOP pin to protect the pack from being over-discharged.

2) Over-discharge Protection Release

The over-discharge protection can be released by connecting a charger when all battery voltages are equal to or higher than the over-discharge detection voltage (V<sub>OD</sub>).

#### (3) Power Down Condition

1) Entering to Power Down Mode

NT1775 enters to the power down mode when over-discharge protection occurs. The VMP pin voltage would be pulled low through the  $R_{VMS}$  resister and the internal circuits would be turned off; therefore, the standby current consumption of NT1775 could be reduced to lower than 100nA (Max.).

2) Power Down Mode Release

The power down mode would be released when a charger is connected with the condition that the VMP pin voltage is around VDD/2 or higher.

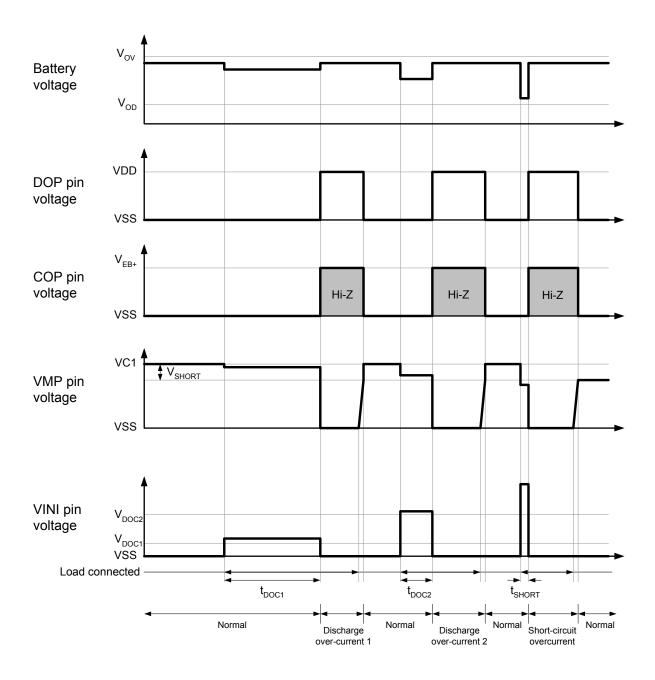

#### (4) Discharge Over-current Condition

1) Discharge Over-current Protection

The NT1775 provides 3 levels of discharge over-current protection - discharge over-current 1, discharge over-current 2 and short circuit protection. When any of the discharge over-current conditions happens, the level of DOP and COP pin would become to "H" from "L" to turn off the MOSFET to cut off the discharge path.

- a) Discharge over-current 1 protection happens when VINI pin voltage is in the condition of  $V_{DOC1} \le V_{VINI} < V_{DOC2}$  and lasts for a delay time longer than the specified delay time ( $t_{DOC1}$ ).

- b) Discharge over-current 2 protection starts when VINI pin voltage is higher than  $V_{DOC2}$  and for lasts for a delay time longer than the specified delay time ( $t_{DOC2}$ ).

- c) Short-circuit protection occurs when VMP pin voltage is in the condition of  $(V_{VMP} V_{VC1}) \le V_{SHORT}$  and for lasts for a delay time longer than the specified delay time  $(t_{SHORT})$ .

In the discharge over-current state, the VMP pin voltage would be pulled up to the VDD level by the internal resister ( $R_{VMD}$ ).

2) Discharge Over-current Protection Release

Any of the discharge over-current/short protections would be released to the normal mode when the load current reduces to the specified current (load resistance  $> 15 \mathrm{M}\Omega$ ) or the voltage drop between VMP and VC1 pins is higher than  $V_{\text{SHORT}}$ . For short-circuit protection, NT1775 may be released to normal or power down mode. It's upon to short-circuit condition. However, it can be awaked from power-down mode as charger is plugged in correctly.

## (5) 0V Battery Charge Function

NT1775 provides a 0 V battery charge function which the batteries can be charged when the charger voltage is higher than  $V_{\text{OCHA}}$ .

#### (6) Delay Time Setting

The over-charge delay time  $(t_{OV})$  depend on the external capacitor's capacitance value to the CCT pin. The over-discharge detection delay time  $(t_{OD})$  and the discharge over-current delay time 1  $(t_{DOC1})$  depend on the external capacitor's capacitance value to the CDT pin. The other delay times, discharge over-current delay time 2  $(t_{DOC2})$ , and short detection delay time  $(t_{SHORT})$  are internally fixed.

```

\begin{array}{cccc} & \text{Min.} & \text{Typ.} & \text{Max.} \\ t_{\text{OV}}[s] &= (5.00, & 10.0, & 15.0) \text{ x } C_{\text{CCT}}[\mu\text{F}] \\ t_{\text{OD}}[s] &= (0.50, & 1.0, & 1.50) \text{ x } C_{\text{CDT}}[\mu\text{F}] \\ t_{\text{DOC1}}[s] &= (0.05, & 0.1, & 0.15) \text{ x } C_{\text{CDT}}[\mu\text{F}] \end{array}

```

Note: The capacitance deviation of the capacitors is not included in the equation above.

## (7) CTL pin

NT1775 provides a CTL pin to control the DOP and COP status. This control function takes precedence over all of the protection functions.

## Conditions set by CTL pin

| CTL Pin | COP Pin        | DOP Pin        |

|---------|----------------|----------------|

| High    | Hi-Z           | VDD            |

| Open    | Hi-Z           | VDD            |

| Low     | Normal status* | Normal status* |

<sup>\*</sup> The all detection circuits take control of the normal status.

## (8) SEL pin

SEL pin is used to switch 4-cell application to the 3-cell. VC4 pin's detection function is prohibited when the SEL pin is connected to the VSS.

## Conditions Set by SEL pin

| SEL Pin | Condition         |

|---------|-------------------|

| High    | 4-cell protection |

| Open    | Undefined         |

| Low     | 3-cell protection |

# **Timing Chart**

## (1) Over-charge Detection, Over-discharge Detection

## (2) Over-current Detection

# **Recommended Application Circuit (Common VSS)**

## **■** For 3-Cell Protection

#### **■** For 4-Cell Protection

# **Recommended Application Circuit (Common VDD)**

## **■** For 3-Cell Protection

#### **■** For 4-Cell Protection

## **Constant for external components (Common VDD/VSS)**

Table Constant for external components

| Symbol             | Parts            | Recommended         | Min.   | Max.  |

|--------------------|------------------|---------------------|--------|-------|

| Charging FET       | P channel MOSFET |                     |        |       |

| Discharging FET    | P channel MOSFET |                     |        |       |

| R <sub>VDD</sub>   | Resistor         | 100Ω * <sup>5</sup> | 51Ω    | 510Ω  |

| R <sub>VC1</sub>   | Resistor         | 100Ω                | 100Ω   | 1ΚΩ   |

| R <sub>VC2</sub>   | Resistor         | 100Ω                | 100Ω   | 1ΚΩ   |

| R <sub>VC3</sub>   | Resistor         | 100Ω                | 100Ω   | 1ΚΩ   |

| R <sub>VC4</sub>   | Resistor         | 100Ω                | 100Ω   | 1ΚΩ   |

| R <sub>co</sub>    | Resistor         | 5.1ΚΩ               | 500Ω   | 10ΚΩ  |

| $R_{DOP}$          | Resistor         | 5.1ΚΩ               | 2ΚΩ    | 10ΚΩ  |

| R <sub>COP</sub>   | Resistor         | 1ΜΩ                 | 0.1ΜΩ  | 1.2ΜΩ |

| $R_{VMP}$          | Resistor         | 20ΚΩ                | 5.1ΚΩ  | 120ΚΩ |

| R <sub>CTL</sub>   | Resistor         | 1ΚΩ                 | 1ΚΩ    | 100ΚΩ |

| R <sub>VINI</sub>  | Resistor         | 1ΚΩ                 | 1ΚΩ    | 100ΚΩ |

| R <sub>SEL</sub>   | Resistor         | 1ΚΩ                 | 1ΚΩ    | 100ΚΩ |

| R <sub>SENSE</sub> | Resistor         | <del></del>         |        |       |

| R <sub>VSS</sub>   | Resistor         | 0Ω * <sup>5</sup>   |        |       |

| C <sub>VC1</sub>   | Capacitor        | 0.1μF               | 0.01μF | 0.1μF |

| C <sub>VC2</sub>   | Capacitor        | 0.1μF               | 0.01μF | 0.1μF |

| C <sub>VC3</sub>   | Capacitor        | 0.1μF               | 0.01μF | 0.1μF |

| C <sub>VC4</sub>   | Capacitor        | 0.1μF               | 0.01μF | 0.1μF |

| Ссст               | Capacitor        | 0.1μF               |        |       |

| C <sub>CDT</sub>   | Capacitor        | 0.1μF               |        |       |

| C <sub>VSS</sub>   | Capacitor        | 2.2μF               | 2.2μF  | 10μF  |

#### Note:

- 1) If the threshold voltage of an FET is lower than 0.4V, the FET may not stop the charging current. If the charger voltage is higher than the withstanding voltage between the gate and source, the FET may be damaged.

- 2) For good noise immunity,  $C_{VC1}$ ,  $C_{VC2}$ ,  $C_{VC3}$ ,  $C_{VC4}$  should be connected to ground.

- 3) For short-circuit protection, the R<sub>CO</sub> should be placed for current limit.

- 4) Using an over-spec  $R_{VC1}$ ,  $R_{VC2}$ ,  $R_{VC3}$ ,  $R_{VC4}$ , may result in over-charge detection voltage and release voltage higher than the expectation.

- If  $R_{VC1}$  has a high resistance, the voltage between VDD and VSS may be higher than absolute maximum rating when a charger is connected reversely since the current flows from the charger to IC.

- 5) The recommended values are 100  $\!\Omega$  and 0  $\!\Omega$  for  $R_{VDD}$  and  $R_{VSS},$  respectively.

Caution: The application circuit above is for reference only. To determine the correct constants, evaluation of actual application is required.

# **Characteristics (Typical Data)**

## 1. Current consumption

# 2. Detection Voltage

## 2.1 Vov vs. Ta

## 2.2 V<sub>OD</sub> vs. Ta

## $2.3\ V_{DOC1}\ vs.\ Ta$

2.2 V<sub>DOC2</sub> vs. Ta

## 3. Detection Delay Time

## 3.1 t<sub>OV</sub> vs. Ta

## $3.2\ t_{OD}\ vs.\ Ta$

## 3.3 t<sub>DOC1</sub> vs. Ta

## 3.2 t<sub>DOC2</sub> vs. Ta

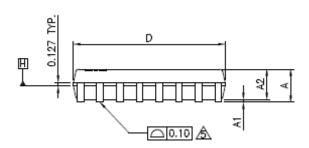

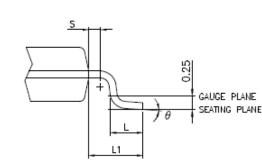

# Package Information TSSOP-16L Dimension

| SYMBOLS   | DIMENSIONS MILLIMETER |          |      |  |

|-----------|-----------------------|----------|------|--|

| STIVIBULS | MIN.                  | NOM.     | MAX. |  |

| Α         | _                     | _        | 1.2  |  |

| A1        | 0.00                  | _        | 0.15 |  |

| A2        | 0.80                  | 1.00     | 1.05 |  |

| b         | 0.19                  | _        | 0.30 |  |

| D         | 4.90                  | 5.00     | 5.10 |  |

| E1        | 4.30                  | 4.40     | 4.50 |  |

| E         | 6.40 BSC              |          |      |  |

| е         |                       | 0.65 BSC |      |  |

| L1        |                       | 1.00 BSC |      |  |

| L         | 0.45                  | 0.60     | 0.75 |  |

| S         | 0.20                  | _        |      |  |

| θ         | 0°                    | _        | 8°   |  |

#### NOTES:

- 1. JEDEC OUTLINE:

- STANDARD : M0-153 ABT REV.F THERMALLY ENHANCED : M0-153 ABT REV.F

- 2. DIMENSION 'D' DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.15 PER SIDE.

- 3. DIMENSION 'E1' DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FALSH OR PROTRUSION SHALL NOT EXCEED 0.25 PER SIDE.

- 4. DIMENSION 'b' DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 MM TOTAL IN EXCESS OF THE 'b' DIMENSION AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OF THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD IS 0.07 MM.

- 5. DIMENSIONS 'D' AND 'E1' TO BE DETERMINED AT DATUM PLANE  $\overline{\mathbb{H}}$ .

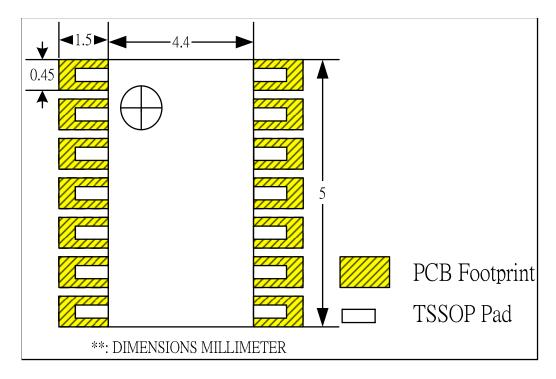

## **Land Pattern Recommendation**

## TSSOP-16L

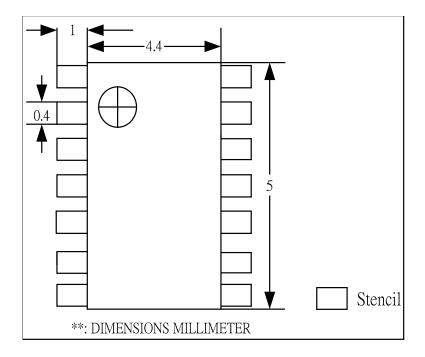

## **Stencil Guideline**

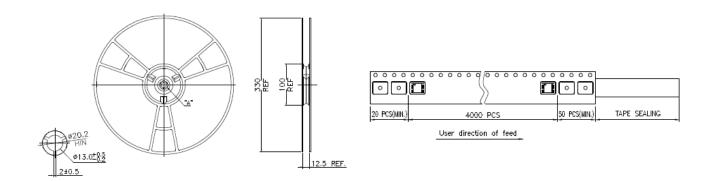

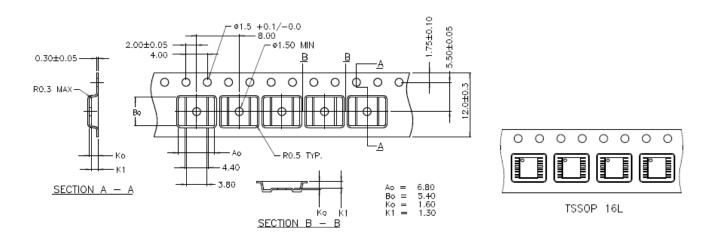

# **Tape and Reel Information**

## Notes:

- 1. 10 sprocket holes pitch cumulative tolerance ± 0.2mm.

- 2. Camber not to exceed 1mm in 100mm.

- 3. Material: Anti-Static Black Advantek Polystyrene.

- 4. Ao and Bo measured on a plane 0.3mm above the bottom of the pocket.

- 5. Ko measured from a plane on the inside bottom of the pocket to the top surface of the carrier

- 6. Pocket position relative to sprocket hole measured as true position of pocket, not pocket hole.

## **Layout Guideline for PCB**

- For 4-layer PCB, the inter-layers are employed as VDD and VSS planes in general. So no matter for common-VDD or –VSS connection, the input filter capacitors can effectively screened out the noise to grand VDD or VSS planes.

- 2. For 2-layer PCB, input capacitors are supposed to be tied to noise-less plane or node. It's strongly recommended to keep VSS as a bulky and complete route as possible for common-VSS connection. Vice versa, a bulky and complete VDD plane or node is better for common-VDD connection. The bulk capacitor between VDD and VSS should be close beside IC.

- 3. Zener diodes are recommended for charging and discharging MOSFET to clamp the spike. An extra zener series-connected with resistor can help ESD and spike clamp for VDD pin.